そういえば KX3 の源発振はDDSではなくて Si570 とかいうプログラマブルオシレータだよな、ということを思い出し、どうやって90度違いのI/Qを作ってるのが気になりました。

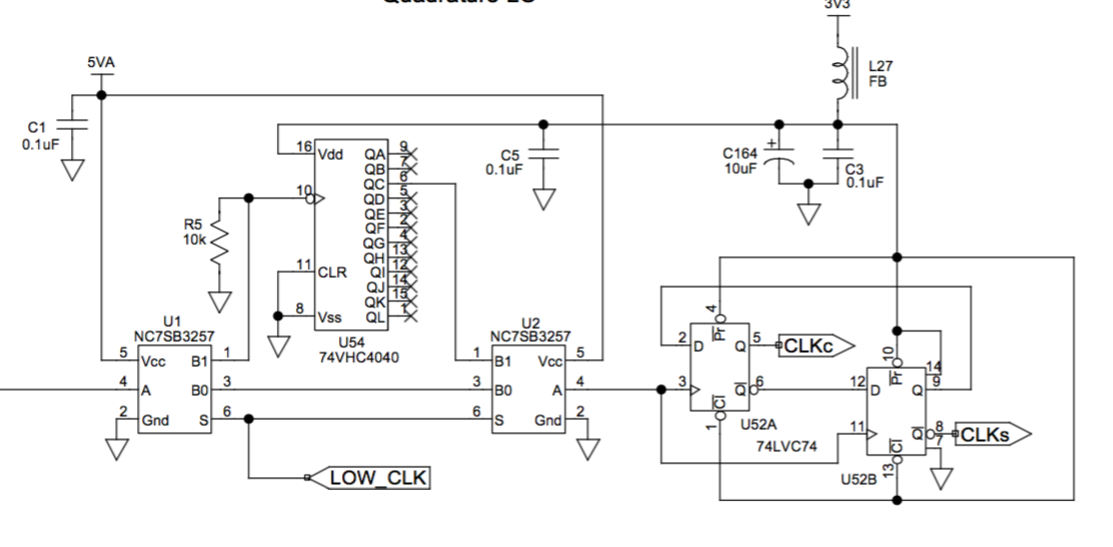

回路図を見ると以下らへんです。左側からきているのが Si570 からのクロックです。

NC7SB3257 はマルチプレクサ、74VHC4040 はカウンタで、ここはバイパス可能な1/8分周器なのでI/Qには関係ありません。

次に出てくる 74LVC74 は Dフリップフロップで、ここでI/Qのクロックを作っているようです。CLKc CLKs がそれぞれ In-phase と Quadrature のようです。

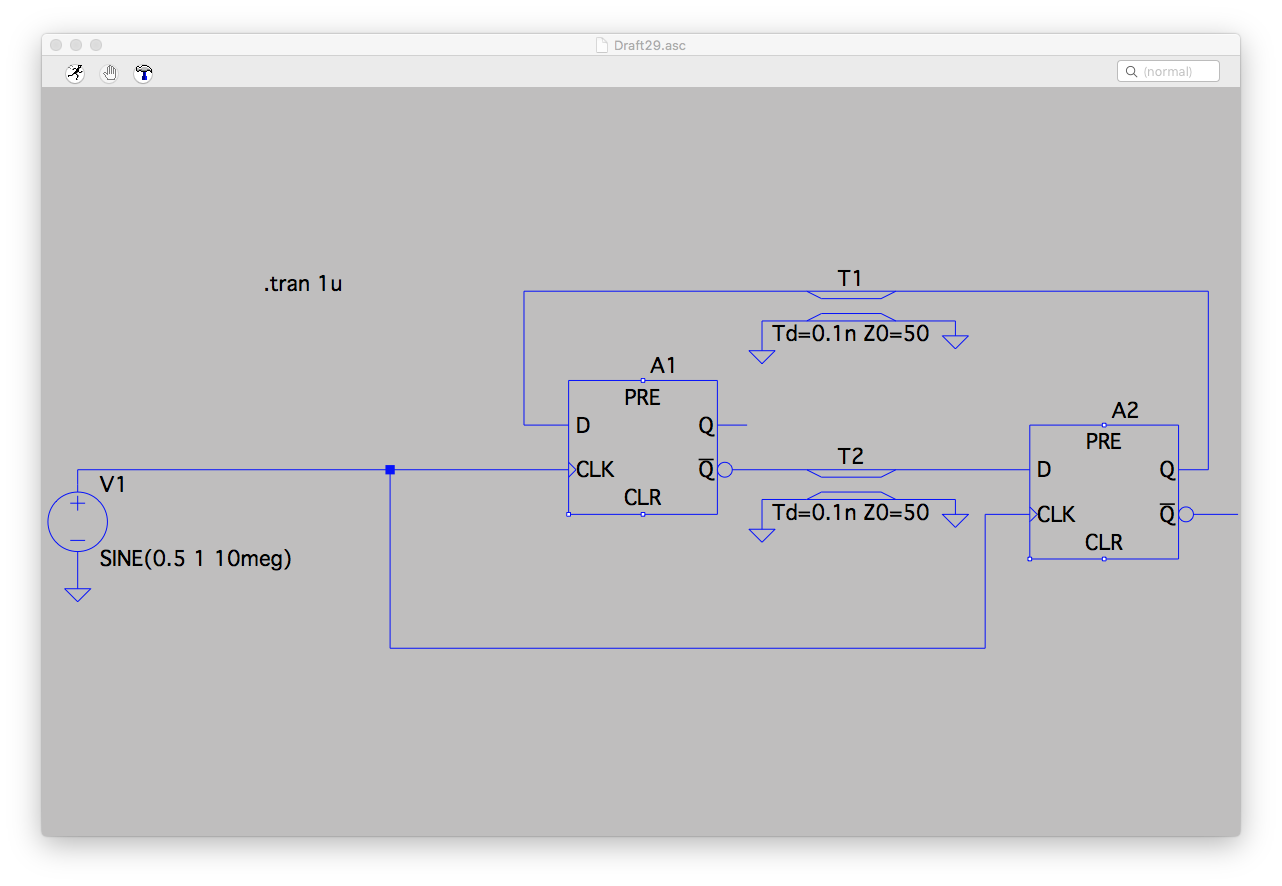

LTSpice でシミュレーションしてみる

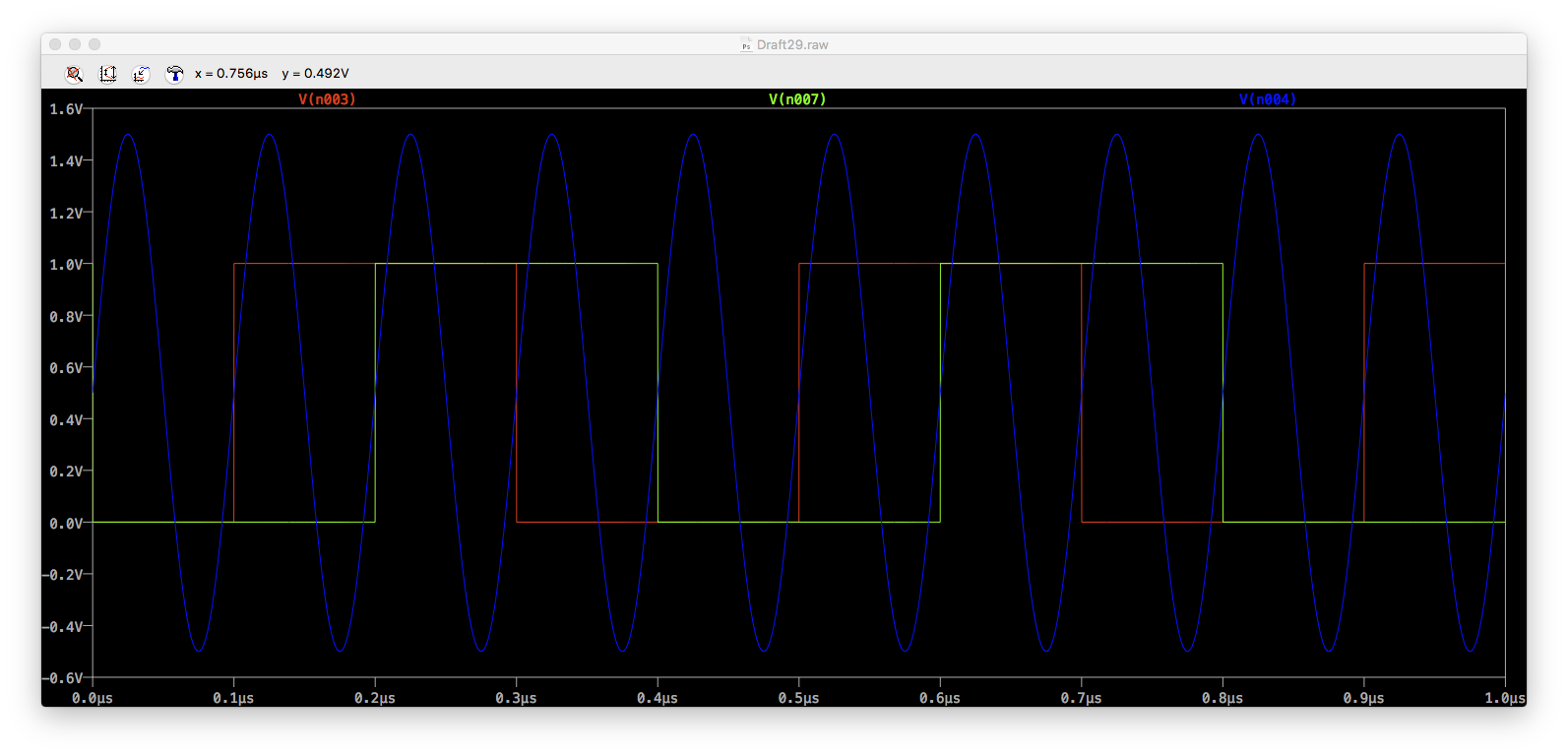

LTSpice に入ってるデジタル素子でシミュレーションしてみました。この素子は理想素子なので、そのまま使うとシミュレーションできませんでした。適当に伝送路に遅延を入れるとなんかそれっぽい波形が出てきました。

4クロックで1つのI/Qクロックに変換される様子がわかります。

源発振の分周比を思い出す

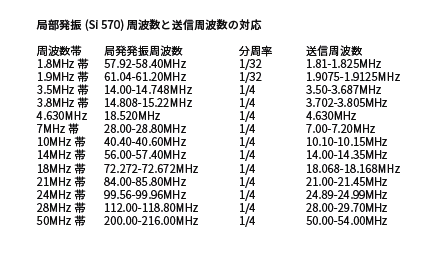

KX3 で無線局免許を更新するとき、送信機系統図に源発振と出力周波数の関係を書いたことを思い出しました。これは電波法の規定で書かなければらないのですが、あまり深く考えていませんでした。以下の表です。

Dフリップフロップを使ったI/Qクロックは上記の通り4分周に相当するので、ここで書いてある表も殆どのケースで 1/4 の分周率になっているのでしょう。

1.8/1.9MHz だと4倍すると7.6MHzぐらいですが、Si570 が 10MHz〜 の発振器なのでさらに分周している、という話のようです。マルチプレクサとカウンタの分周は1.8/1.9MHz用というわけのようです。

DフリップフロップによるI/Qクロック生成のメリット/デメリット

メリット

- 実質デジタル処理なので広い帯域で正確に90度位相差を得られる

- クロック発信源が1つだけで良い

デメリット

- 欲しい周波数の4倍の源発振器が必要

- 矩形波出力 (デメリットかどうかは場合による)

200MHz ぐらいまでの発振器は安いのがいくらでもあるのですが、ここを超えると急に高価になる気がするので、50MHz で使うかどうか、DDS2台にするかどうか大きく判断が別れそうです。とはいえ、基本的にはDDS2台よりも安価で省電力そうです。