「コイルとコンデンサは電圧と電流の位相差を90度進めさせる/遅れさせる」という説明を良く見ますが、どうも直感的に理解できていませんでした。電圧と電流の位相差が±90度か0度しかとらないという話ではないだろうし、「途中の位相はないの?」と思ってしまうのです。この説明の意味がわからない、という意味です。

疑問の詳細

コイルとコンデンサの組合せで共振回路をつくった場合、電圧と電流の位相差はゼロになるはずです。ではすこしだけ共振していない場合はどうなるのでしょうか? 現実的には殆どの場合共振していないはずです。

「すこしだけ共振していない状態」であっても回路全体としてはインダクティブであるかキャパシティブであるかのどちらかであり、±90度の位相差は起こっているはずです。

でも現実問題としては回路全体で観測できる電圧と電流の位相差は必ずしも±90度ではありません。少しだけ共振していない場合は殆ど位相はずれていません。

途中の位相はどこいった?

式を使って「このように位相がずれます!!」というのは置いといて「途中の位相はどこいった?」という疑問だけ解決します。

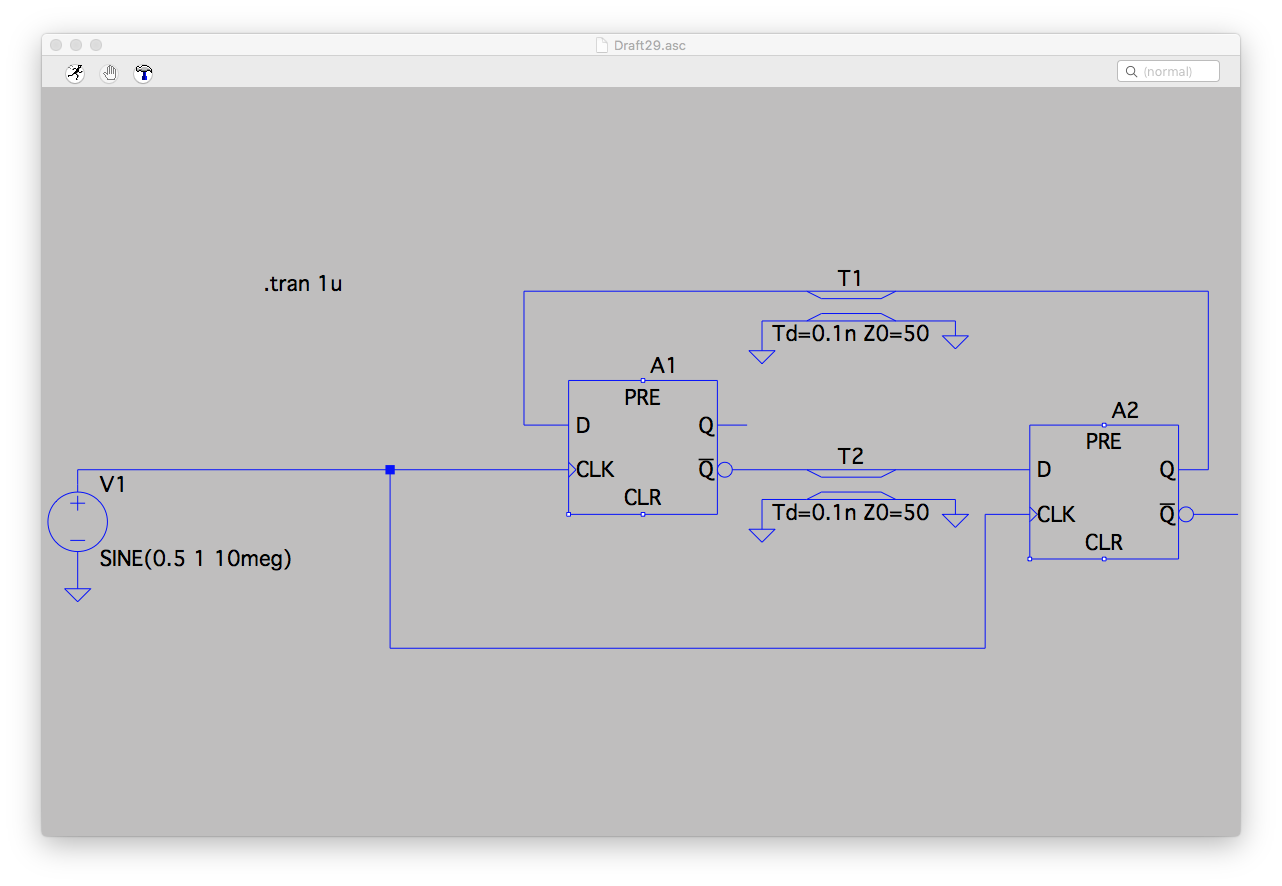

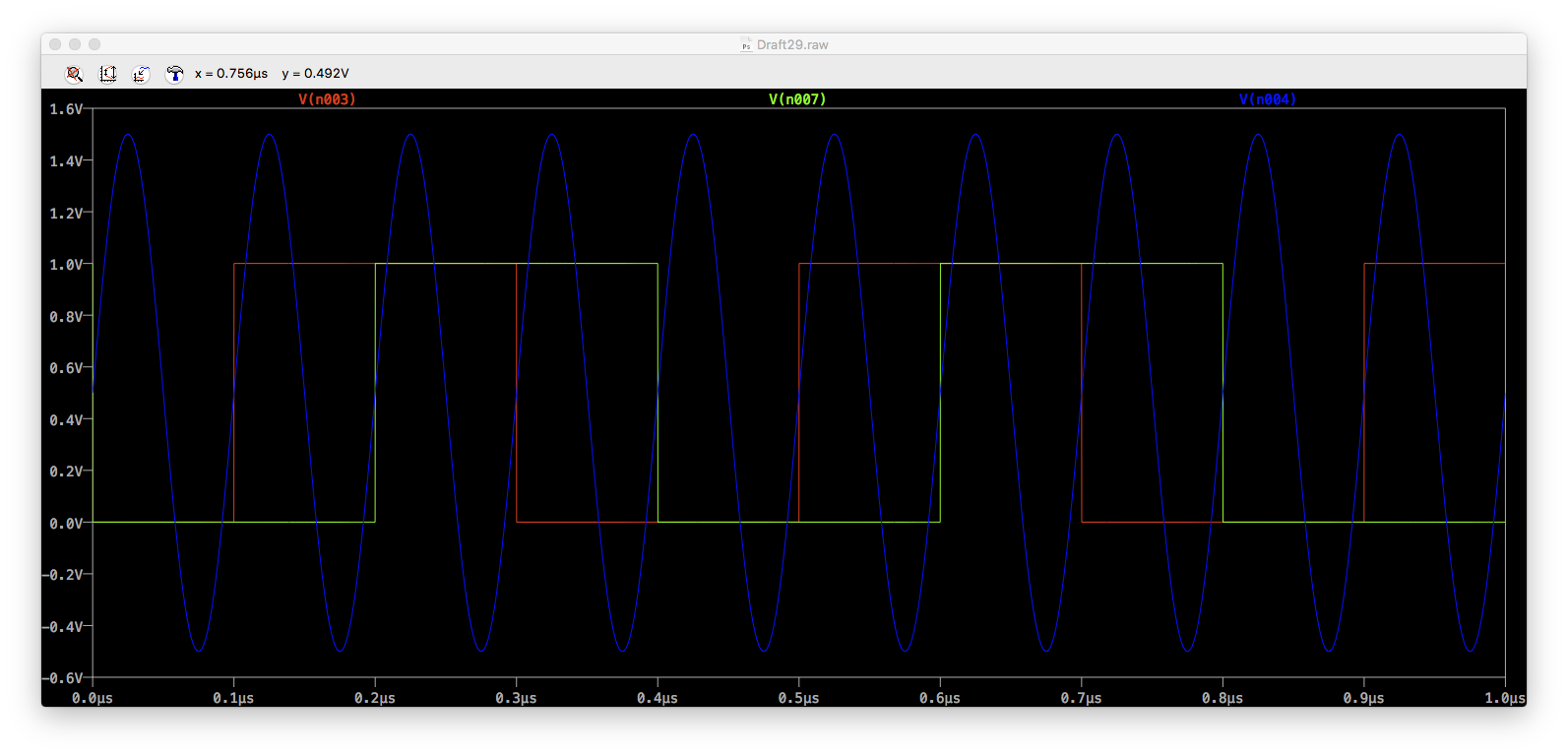

純リアクタンス成分に関していえば、確かに±90度の位相差を常に起こしています。これはコイルとコンデンサだけで構成された回路なら回路全体に対してもあてはまります。「少しでも」コイルやコンデンサがあれば必ず±90度の位相差が起こっています。コイルとコンデンサの複合回路でも、共振していなければ必ず±90度の位相差が起きます。これはシミュレーションでも確認できます。

しかし実際の観測される位相は抵抗成分も含めて考える必要があります。これにより回路全体を見たときの位相差は任意の角度をとります。

全体として、抵抗成分が少なければ少ないほど-90度か+90度に近付き、リアクタンス成分が少なければ少ないほど、0度に近付いていきます。

複素平面上で見たときも、純リアクタンス成分は全体としても±90度にしかならないが、抵抗が加わった瞬間、合成された絶対値はいろんな別の角度をとりうることがわかります。

つまり

「コイルとコンデンサは電圧と電流の位相差を90度進めさせる/遅れさせる」というような説明は、純粋にそのコンポーネントの理想的な電圧の電流の関係をいっていて、抵抗成分を含めたことは言ってないわけでした。この説明、何度も何度も目にしてきたのに、何を言ってるのかわかりませんでしたが (途中の位相もあるよな?と思っていた)、ようやく意味がわかった気がします。

そして思いますが、この説明の仕方は筋が悪いと思います。現実のコイルやコンデンサには必ず無視できないほどの抵抗成分がありますから、これらのコンポーネントだけで回路を構成したとしても必ずしも位相差は±90度のどちらかになるというわけではないはずです。コイルやコンデンサと言うのではなくて「純リアクタンス成分は〜」とかで書いたほうが正確だと思いました。